Next: Implantación del hilo V86

Up: Diseños del monitor y

Previous: Diseño Padre-hijo con memoria

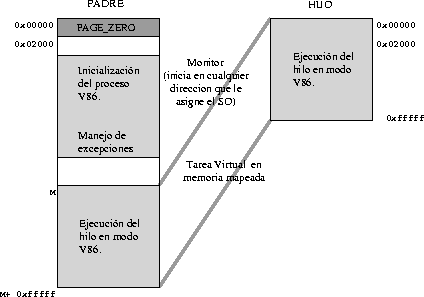

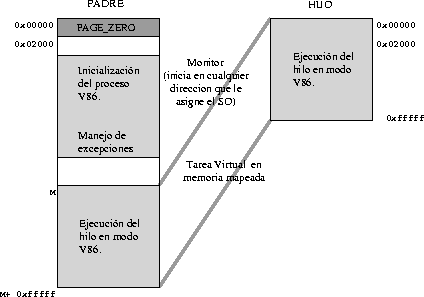

Para no tener que poner a concurso el primer megabyte del espacio de

direcciones del proceso monitor, se puede implantar la aplicación cargando

el código del monitor en cualquier lugar de su espacio de direcciones, y

crear la tarea hija, donde se ejecutará el hilo V86, con su primer

espacio de direcciones mapeadas en algún espacio de direcciones

contíguas de un megabyte, en la tarea monitor, para que el proceso

monitor actualize directamente esta memoria. Cuando nos referimos a mapear

decimos que la memoria se comparte, pero tiene diferentes direcciones para

la tarea hija (donde el rango va de 0 a 1 megabyte) y para la tarea padre

(donde el rango va de M a M+1 megabyte, y M es una dirección que es

múltiplo de 0x100000), como se puede apreciar en la figura

6.5. Este modelo conviene, debido a que el proceso V86 se ejecuta en el primer megabyte de su espacio de direcciones.

Figure 6.5:

Diseño Padre-Hijo con memoria mapeada

|

El proceso monitor pueder hacer la simulación de las instrucciones

especiales leyendo y escribiendo directamente en su propio espacio de

direcciones, teniendo la garantía de que las modificaciones realizadas

también se han hecho en la tarea V86.

Este modelo parece ser el más adecuado, ya que este manejo de memoria se

contempla en Mach, con los denominados objetos de memoria, sin embargo nunca

se pudo probar ya que la versión de Mach para NeXTSTEP no tiene implantados

los objetos de memoria.

Next: Implantación del hilo V86

Up: Diseños del monitor y

Previous: Diseño Padre-hijo con memoria

Amilcar Meneses

2002-10-03