|

Este esquema tiene la facilidad de que no crea un nuevo proceso, en vez de esto, sólo crea un hilo extra (hilo V86) y construye un bloque de memoria (en vez de crear la tarea V86). Además el proceso monitor puede actualizar directamente la parte baja del espacio de direcciones para llevar acabo la simulación de las instrucciones especiales, debido a que son direcciones de memoria de su propia tarea Mach.

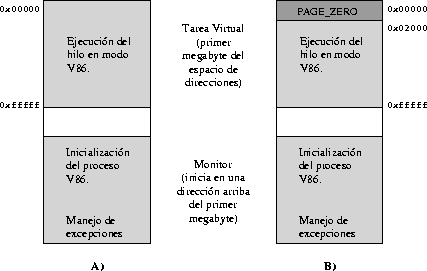

Esta parece ser la solución idónea, sin embargo, en la versión de Mach que se esta trabajando, el sistema operativo NeXTSTEP reserva la primera página de memoria (llamada PAGE_ZERO) para almacenar las instrucciones y estructuras de los MachObjects6.4 y para atender a los apuntadores cuando tienen el valor NULL, como se aprecia en la figura 6.3B. Esta página de memoria tiene permisos de lectura escritura y ejecución sólo para el sistema operativo, el usuario no puede cambiar estas protecciones.