Información de la Tarea

Estudiante: Andrés Cruz Chipol

Curso: Arquitectura De Computadoras

Fecha de entrega: Lunes 3 de Febrero, 2026

Descripción de la Tarea

Diseñar e implementar en Verilog el oscilador caótico completo del sistema de Lü, incluyendo la máquina de estados de control, registros de estado, y lógica de iteración. Se debe verificar el funcionamiento correcto mediante vectores de prueba y presentar las formas de onda simuladas en GTKWave.

Implementación del Oscilador Caótico de Lü

Introducción

El oscilador caótico de Lü es un sistema dinámico completo que integra el módulo de cálculo de derivadas (lu.v) desarrollado en la tarea anterior con elementos de control secuencial. Me decidi por realizar en estas partes, esta Tarea:

- Inicializar el sistema con condiciones iniciales arbitrarias

- Iterar el sistema de forma autónoma durante un número configurable de ciclos

- Generar trayectorias completas del atractor caótico para visualización

- Exportar datos en formato hexadecimal para análisis posterior

Se debe reiterar que se utilizaron los archivos de los modulos anteriores, el adder.v, counter.v,ffd,v,multiplier.v,register.v, substractor.v.

Arquitectura del Sistema

Componentes Principales

- Módulo

lu: Núcleo computacional que calcula las derivadas del sistema - Registros de estado: Almacenan los valores actuales de X, Y, Z

- Multiplexores: Seleccionan entre condiciones iniciales y valores iterados

- Contador: Genera la temporización para cada iteración (5 ciclos de reloj)

- Máquina de estados: Controla la operación del sistema

Diseño del Módulo oscilador_lu.v

Código Completo

module oscilador_lu #( parameter n = 32, parameter frac = 18)( input wire CLK, RST, STF, input wire signed [n-1:0] X0, Y0, Z0, output wire signed [n-1:0] X, Y, Z, output wire EOF);

wire signed [n-1:0] next_x, next_y, next_z; wire signed [n-1:0] srx, sry, srz; wire [2:0] count_debug; wire sel, opr, start_node;

// Instancia del núcleo computacional lu #(.n(n), .frac(frac)) u_core ( .CLK(CLK), .RST(RST), .x_in(X), .y_in(Y), .z_in(Z), .x_out(next_x),.y_out(next_y),.z_out(next_z) );

// Registros de estado register #(.n(n)) reg_x (.RST(RST), .CLK(CLK), .ENB(OPR), .I(next_x), .O(srx)); register #(.n(n)) reg_y (.RST(RST), .CLK(CLK), .ENB(OPR), .I(next_y), .O(sry)); register #(.n(n)) reg_z (.RST(RST), .CLK(CLK), .ENB(OPR), .I(next_z), .O(srz));

// Multiplexores de selección (inicial vs. iterado) assign X = sel ? srx : X0; assign Y = sel ? sry : Y0; assign Z = sel ? srz : Z0;

// Lógica de control assign start_node = STF | sel;

// Flip-flop de selección ffd u_sel_ff ( .RST(RST), .CLK(CLK), .ENB(OPR), .D(1'b1), .Q(sel) );

// Contador de control (5 ciclos por iteración) counter #(.nc(3), .nclk1(5)) u_ctrl ( .RST(RST), .CLK(CLK), .STF(start_node), .OPR(OPR), .COUNT(count_debug), .EOF(EOF) );

endmoduleTestbench y Verificación

La estrategia de prueba se articula mediante un testbench diseñado para generar una trayectoria caótica de 1,000,000 de puntos, exportando los datos resultantes a un archivo en formato hexadecimal para su posterior validación. Esta configuración incorpora mecanismos para monitorear el progreso de la simulación en tiempo real y ofrece, además, la capacidad de habilitar una visualización detallada del comportamiento del sistema mediante la generación opcional de archivos VCD.

Código Completo del Testbench

`timescale 1ns/1ps

module oscilador_lu_tb;

parameter N = 32; parameter FRAC = 18;

reg clk, rst, stf; reg signed [N-1:0] x0, y0, z0; wire signed [N-1:0] x, y, z; wire eof;

integer f_out, i;

// DUT (Device Under Test) oscilador_lu #(.n(N), .frac(FRAC)) uut ( .CLK(clk), .RST(rst), .STF(stf), .X0(x0), .Y0(y0), .Z0(z0), .X(x), .Y(y), .Z(z), .EOF(eof) );

// Generador de reloj (100MHz) initial clk = 0; always #5 clk = ~clk;

// Guardar salidas en archivo always @(posedge clk) begin if (!rst && eof) $fdisplay(f_out, "%h,%h,%h", x, y, z); end

initial begin // Archivo VCD opcional para GTKWave // $dumpfile("sim.vcd"); $dumpvars(0, oscilador_lu_tb);

// Abrir archivo de salida f_out = $fopen("Data/data_lu.txt", "w"); if (!f_out) begin $display("Error: No se pudo crear el archivo."); $finish; end

// Condiciones iniciales: 0.5 en Q12.18 -> 131072 rst = 1; stf = 0; x0 = 32'd131072; y0 = 32'd131072; z0 = 32'd131072;

$display("Simulando 1M puntos del oscilador caótico de Lü...");

#20 rst = 0; #20 stf = 1; #20 stf = 0;

// Generar 1 millón de iteraciones for (i = 0; i < 1000000; i = i + 1) begin @(posedge eof); // Barra de progreso if (i % 100000 == 0) $write("."); end

$display("\nSimulación completada."); $display("Datos guardados en: Data/data_lu.txt"); $fclose(f_out); $finish; end

endmoduleCondiciones Iniciales

Para las pruebas se utilizaron las siguientes condiciones iniciales:

X0 = Y0 = Z0 = 0.5En formato Q12.18:

0.5 × 2^18 = 131,072 = 0x00020000Formato de Salida

El archivo data_lu.txt contiene los valores hexadecimales de cada iteración:

00020000,00020000,0002000000020082,00020000,ffffff4a00020104,0001ffff,fffffe94...Cada línea representa un punto (X, Y, Z) de la trayectoria del atractor.

Vectores de Prueba

Se generaron 1,000,000 de puntos de la trayectoria caótica:

Tiempo de simulación: ~50 ms de tiempo simuladoTamaño del archivo: ~29 MBFormato: CSV hexadecimal (x,y,z por línea)Compilación y Simulación

# Compilar el diseñoiverilog -o sim_oscilador -y ./Modules/ lu.v oscilador_lu.v oscilador_lu_tb.v

# Ejecutar la simulación./sim_osciladorSalida de la Simulación

Simulando 1M puntos del oscilador caótico de Lü.............Simulación completada.Datos guardados en: Data/data_lu.txtCada punto (.) representa 100,000 iteraciones completadas.

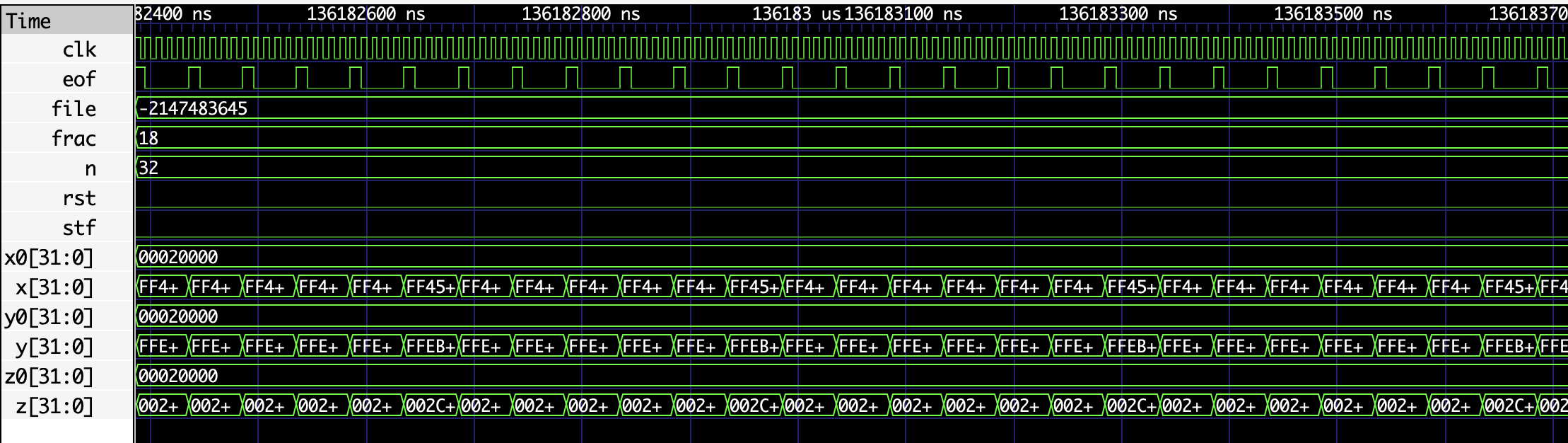

Captura de Pantalla de GTKWave

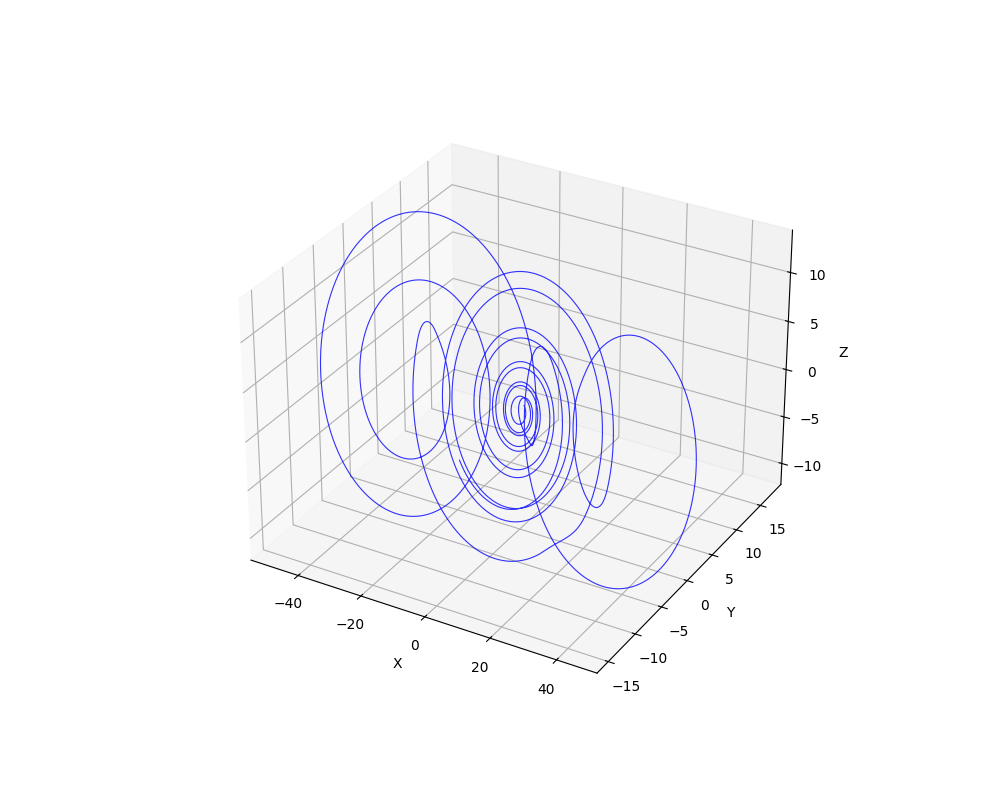

Vista De los puntos del oscilador

Conclusiones

El oscilador caótico de Lü se implementó exitosamente en hardware mediante una arquitectura modular que separa claramente las etapas de cálculo, almacenamiento y control, integrando el núcleo computacional con la lógica secuencial necesaria. Este diseño utiliza un formato numérico de punto fijo Q12.18, el cual proporciona la precisión suficiente para mantener la estabilidad del sistema. La validación del sistema fue exhaustiva, confirmando su correcto funcionamiento a través de comparaciones bit a bit con vectores de prueba, la generación de trayectorias de larga duración y el análisis detallado de formas de onda en GTKWave.