|

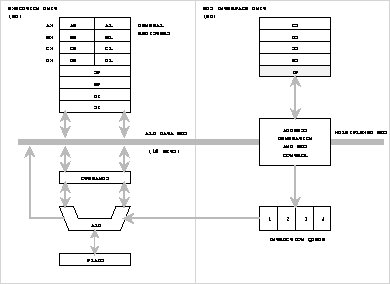

Estos microprocesadores tiene 2 procesadores conectados internamente, como se puede apreciar en la figura 2.1, estos procesadores son:

La unidad de ejecución (EU) se encarga de realizar las operaciones aritméticas y lógicas, además de proporcionar las direcciones lógicas al BIU --una dirección lógica está formada de dos direcciones, la primera indica el segmento en el cual se está trabajando y la otra indica el offset, o desplazamiento, de este segmento; esto es segment:offset--.

La EU tiene una unidad aritmética lógica (ALU) de 16 bits, un registro de banderas y un conjunto de registros de propósito general. El registro de banderas contiene 6 banderas de estado (que la EU manipula para

indicar el estado del resultado de una operación lógica o

aritmética) y 3 banderas de control que se pueden manipular por los

programas para alterar las operaciones del procesador (figura 2.2).

La unidad de interfaz con el Bus (BIU) es la responsables de la comunicación

externa del procesador. Esta unidad de proceso se encarga de traducir las

direcciones lógicas a direcciones físicas de la memoria con ayuda de los

registros de segmento DS, SS, ES, CS e IP. Para convertir una dirección

lógica en una dirección física el BIU corre el valor del registro de

segmento 4 posiciones a la izquierda (que es equivalente a multiplicar por

16h) y suma el valor del offset para obtener un valor de 20 bits

necesarios, como se muestra en la figura 2.3.

Los segmentos en la memoria pueden estar translapados, contiguos o disjuntos. El 8086 trabaja con un modelo de memoria circular, esto es, cuando la operación de translado de memoria lógica a memoria física sobrepasa el megabyte de memoria, entonces se direcciona la parte inicial de la memoria física.

La dirección de la siguiente instrucción que se ejecutará es CS:IP (Code Segment: Instruction Pointer). Para incrementar la eficiencia, en períodos donde la EU está ocupada ejecutando instrucciones, el BIU se adelanta a una petición de intrucción del EU y busca más instrucciones de la memoria. Las instrucciones se almacenan en una cola de instrucciones de 4 bytes para el 8088 y 6 bytes para el 8086. Bajo muchas circunstancias las colas contienen al menos 1 byte instrucción y el EU no tiene que esperar a que se busquen nuevas instrucciones. Las instrucciones almacenadas en la cola son adyacentes en la memoria, así, cuando se ejecuta una instrucción que transfiere el control a otra localidad el BIU limpia la cola y busca las nuevas instrucciones desde la nueva dirección.

El 8088/8086 tienen un sistema de interrupciones simple y versátil , estos procesadores pueden manejar hasta 256 interrupciones diferentes. Las entradas de las interrupciones se encuentran almacenadas el vector de interrupciones en la parte baja de la memoria. A cada interrupción se le asocia una doble palabra. Cada palabra doble corresponde al CS:IP de la subrutina que la interrupción invoca. Las primeras cinco interrupciones se utilizan para los siguientes errores: división por cero, paso sencillo (trap), interrupción no enmascarable, punto de ruptura y sobreflujo. El 8088/8086 no distingue entre las interrupciones generadas por hardware y por las interrupciones generadas por la instrucción INT.